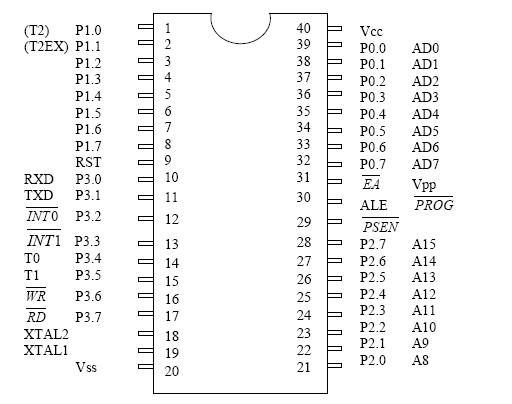

Raspored i značenje pinova mikrokontrolera Intel 8051

Mikrokontroler je jedno od najvećih tehničkih dostignuća koje je obeležilo dvadeseti vek. Sa napredkom tehnologije rastao je stepen integracije integrisanih kola, što je dovelo do pojave prvih mikroprocesora i mikrokontrolera. Prvi mikroprocesor je proizveden 1971. godine. Bio je to 4-bitni Intel 4004. U familiji INTEL-ovih mikrokontrolera izvedenih u vidu jednog čipa mikrokontroler, INTEL 8051 je sintetizovan namenski da služi kao procesor u sistemima digitalnog upravljanja.

Mikrokontroler je jedno od najvećih tehničkih dostignuća koje je obeležilo dvadeseti vek. Sa napredkom tehnologije rastao je stepen integracije integrisanih kola, što je dovelo do pojave prvih mikroprocesora i mikrokontrolera. Prvi mikroprocesor je proizveden 1971. godine. Bio je to 4-bitni Intel 4004. U familiji INTEL-ovih mikrokontrolera izvedenih u vidu jednog čipa mikrokontroler, INTEL 8051 je sintetizovan namenski da služi kao procesor u sistemima digitalnog upravljanja.

Slika br.1 Raspored i oznake pinova

Od 1 do 8 – Port 1: Svaka od ovih nožica može da se koristi kao ulazni ili izlazni priključak.

9 – Reset: Visok logički nivo na ovom ulazu resetuje sve interne registre (registre dovodi u stanje 00000000), sa sledećim izuzecima:

- P0, P1, P2 i P3 (izlazni registri svih spoljnih portova) se dovode u stanje 11111111

- SBUF se ne menja

- SP se dovodi u stanje 00000111 (07h)

- Neki biti u registrima IP, IE i PCON fizički ne postoje, pa tako ne mogu ni da se resetuju

- Sadržina celog internog RAM-a se ne menja

Najvažnija posledica aktiviranja RESET ulaza je da se PC (Program Counter) resetuje, tako da će započeti izvršavanje programa od adrese 0000h.

Od 10 do 17 – Port 3: Ako se koristi kao univerzalni ulaz ili izlaz, po svemu je sličan portu 1, ali na svakoj nožici ima još po neku specijalnu funkciju:

- 10 (P3.0) RXD – Serijski ulaz za asinhronu komunikaciju (mod 1, 2 i 3) ili serijski izlaz za sinhronu komunikaciju (mod 0)

- 11 (P3.1) TXD – Serijski izlaz za asinhronu komunikaciju (mod 1, 2 i 3) ili taktni (clock) izlaz sa sinhronu komunikaciju (mod 0)

- 12 (P3.2) INT0 – Ulaz za prekid (interapt) 0

- 13 (P3.3) INT1 – Ulaz za prekid (interapt) 1

- 14 (P3.4) T0 – Ulaz spoljnjeg takta za brojač 0

- 15 (P3.5) Tl – Ulaz spoljnjeg takta za brojač 1

- 16 (P3.6) WR – Signal za upis u spoljnu memoriju

- 17 (P3.7) RD – Signal za čitanje iz spoljne memorije

18 i 19 – X2 i X1: Izlaz i ulaz internog oscilatora. Ako se koristi kvarc-kristal za stabilizaciju učestanosti oscilatora (što je najčešći slučaj), on se vezuje za ove dve nožice, s tim što na svaku nožicu (prema masi) treba dodati još po jedan kondenzator od 20-40pF. Ovoje potrebno da bi se sprečilo oscilovanje na nekom višem harmoniku. Opseg učestanosti je od 1 do 12 MHz, a izrañuju se i mikrokontroleri koji rade i na znatno višim frekvencijama.

20 – Masa

Od 21 do 28 – Port 2 ili adrese A8 do A15: Ako se koristi mikrokontroler sa internim ROM-om i nema spoljnjeg ROM- ili RAM-a, mogu se koristiti sve linije ovog porta kao univerzalni ulazi ili izlazi. Ako se koristi spoljna memorija, onda su ovo visoki adresni izlazi, od A8 do A15. U tom slučaju, čak i ako se koriste samo neke adrese, preostale nožice ovog porta ne mogu da se koriste kao ulazi ili izlazi.

29 – PSEN: Program Select Enable (aktiviranje spoljašnjeg ROM-a): Normalno se ovaj izlaz spaja sa CS ili OE ulazom na spoljnom EPROM-u, jer ga mikrokontroler aktivira (dovodi na nizak nivo) svaki put kad čita bajt iz programske memorije (za kontrolu spoljašnjeg RAM-a se koriste druge nožice).

30 – ALE: Address Latch Enable (Upis u adresni registar): Da bi sve željene funkcije spakovao u standardno kućište od samo 40 nožica, Intel je morao da pribegne multipleksiranju nekih signala. Tako je port P0 dobio dve funkcije: izlazne adrese A0-A7 i ulaz/izlaz podataka D0-D7. Pre svakog očitavanja programa iz spoljne memorije ili prozivanja RAM-a mikrokontroler na P0 prosleñuje niži bajt adresnog registra i aktivira izlaz ALE. Spoljni registar (najčešće LATCH registar tipa 373 ili 573 iz TTL 74xx familije) na visok nivo ALE memoriše stanje P0, a izlazi ovog registra se koriste kao A0-A7. U drugom delu mašinskog ciklusa mikrokontrolera P0 se koristi kao magistrala podataka (Data Bus).

31 – EA: External Access (Pristup spoljašnjem ROM-u): Ako je ovaj ulaz nizak, mikrokontroler će sve instrukcije čitati iz spoljnog ROM-a, bez obzira da li ima interni ROM, a ako je visok, prvih 4 KB (8051, 8751) ili 8 KB (8052, 8752) će čitati iz internog, a sve ostalo do kraja adresnog prostora iz eksternog ROM-a. Ako se koristi 8031 ili 8032, na ovaj ulaz treba uvek dovesti nizak nivo (najbolje je spojiti ga sa masom).

od 32 do 39 – Port 0, Adrese A0-A7 ili magistrala podataka: Slično portu P2, i port P0 može da se koristi kao univerzalni ulaz i izlaz samo ako se ne koristi spoljna memorija. Ako se koristi, tada je P0 adresni izlaz za A0-A7 kad je ALE visok, a magistrala podataka (Data Bus) kada je ALE nizak.

40 – Napajanje +5V